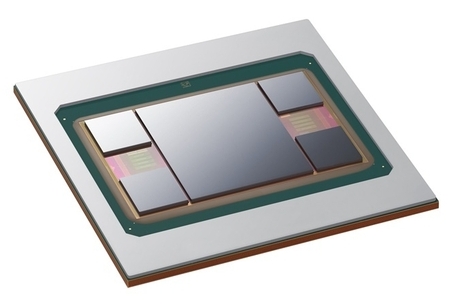

삼성전자는 로직 칩과 4개의 HBM(High Bandwidth Memory) 칩을 하나의 패키지로 구현한 독자 구조의 2.5D 패키지 기술 ‘I-Cube4’를 개발했다고 6일 밝혔다.

‘I-Cube’는 실리콘 인터포저 위에 CPU, GPU 등의 로직과 HBM을 배치해 하나의 반도체처럼 동작하도록 하는 이종 집적화 패키지 기술이다.

이를 통해 복수의 칩을 1개의 패키지 안에 배치해 전송 속도는 높이고, 패키지 면적은 줄일 수 있다.

삼성전자는 ‘I-Cube4’에 실리콘 인터포저(Si-Interposer)를 적용해 초미세 배선을 구현했으며, 반도체 구동에 필요한 전력도 안정적으로 공급할 수 있도록 했다.

일반적으로 패키지 안에 실장하는 반도체 칩이 많아질수록 인터포저의 면적도 함께 증가해 공정상의 어려움도 커진다.

삼성전자는 100 마이크로미터 수준의 매우 얇은 인터포저가 변형되지 않도록 재료, 두께 등 다양한 측면에서 반도체 공정·제조 노하우를 적용했다.

또한 ‘I-Cube4’에 몰드를 사용하지 않는 독자적인 구조를 적용해 열을 효율적으로 방출하도록 했다.

삼성전자는 또한 패키지 공정 중간단계에서 동작 테스트를 진행해 불량을 사전에 걸러내고, 전체 공정 단계를 줄여 생산기간을 단축했다.

삼성전자 파운드리사업부 마켓전략팀 강문수 전무는 “고성능 컴퓨팅 분야를 중심으로 차세대 패키지 기술의 중요성이 높아지고 있다”며 “삼성전자는 ‘I-Cube2’ 양산 경험과 차별화된 ‘I-Cube4’ 상용화 기술 경쟁력을 기반으로 HBM을 6개, 8개 탑재하는 신기술도 개발해 시장에 선보이겠다”고 밝혔다.

한편, 삼성전자는 2018년 로직과 2개의 HBM을 집적한 ‘I-Cube2’ 솔루션을 선보였으며, 2020년에는 로직과 SRAM을 수직 적층한 ‘X-Cube’ 기술을 공개하며 차세대 패키지 기술도 차별화하고 있다.